10 nm, 7 nm, 5 nm… founders never stop reducing the “fineness of engraving” of transistors. This small figure is of great importance in the technological and commercial war between the founders, fueled by the demands of ever more demanding customers. TSMC seems to have won the 7nm battle, which it has just started volume production, and which the future Apple A12 chip should take advantage of. Which does not mean that the Taiwanese founder will win the war…

The manufacture of integrated circuits is a slow and complex process, which begins with a wafer, a disk of extremely pure silicon 1 . Doping, deposition of a resin layer, etching, heat treatment, thin layer coating, cutting, encapsulation… transforming the wafer into chips requires dozens of steps. Etching is the most important moment: the components are "sculpted" or "drawn" by various processes, such as the chemical treatment of the silicon substrate, or the photolithography of a thin layer of photoresist.

The improvement of engraving techniques makes it possible to design ever smaller components. Be careful though: when we talk about “engraving fineness of 10 nm”, we are only talking about the manufacturing process, and not the size of the components 2 . The same etching fineness of 10 nm will produce components of different sizes depending on the technologies used and the type of component. Components produced with TSMC's 7nm process, for example, are not much smaller than those produced with Intel's 10nm process.

But it doesn't matter: all founders, whether they use this or that process with this or that material for this or that use, work to reduce the fineness of engraving. It is not only a question of increasing the profitability of a wafer, but also and above all of increasing the density and the energy yield of the chips 3 . The Apple A11 Bionic has 4,300,000,000 transistors, 1,869,565 times more than the first microprocessor, the Intel 4004. If it were still etched at 10µm, it would cover the area of a large living room, but since it is etched at 10 nm, it measures less than 90 mm^2.

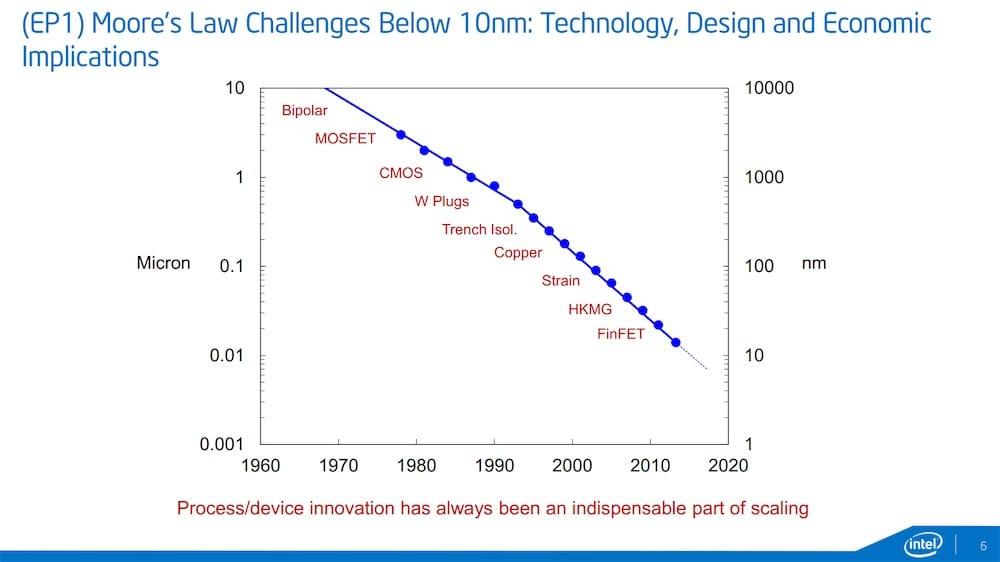

Each reduction in etching fineness forms a process, or node, with contours defined by the International Technology Roadmap for Semiconductors (ITRS). Why do we go from 22 to 14 nm, from 14 to 10 nm, from 10 to 7 nm? Because the ITRS wants to follow a ratio of √1/2 to one, which corresponds to doubling the number of components with equal surface area. Set a new node every two years, and you can continue to pass off Gordon Moore's predictions as hard law. Except that this rhythm is more and more difficult to maintain.

The passage below 22 nm required the abandonment of planar transistors, in favor of "3D transistors" such as FinFETs. Going below 7 nm will undoubtedly require the use of new FinFET transistors or GAA transistors, or even the abandonment of silicon. Smelters are starting to come up against physical limits, such as the tunnel effect, and will soon be working on the scale of the atom. Research on atomic transistors, and further on quantum electronics, is still in its infancy.

But back to the present. Intel is keen to finalize its 10 nm process, now scheduled for the end of 2018 or even 2019. The Santa Clara foundry is clearly behind on its roadmap, which provided for the switch to 10 nm for the end of 2016, but not (yet) outpaced by the rest of the industry. For the same process, Intel's technologies produce denser circuits than competing technologies. Provided it capitalizes on the experience acquired to make 10 nm profitable and develop 7 nm, Intel will be able to stay in the race.

But its competitors are already planning to put 5 nm processes into production next year. Samsung made the bet to finalize its 7 nm process later than its competitors to test photolithography with extreme ultraviolet radiation, which will be imperative to the development of 5 nm processes, and thus gain the upper hand over TSMC and GlobalFoundries. The open ground, these two fought a fierce battle on 7 nm: TSMC won and should recover the contracts to manufacture AMD processors and graphics cards.

The other big match is played on the mobile field, again with TSMC, but this time against Samsung. Qualcomm, which wants to benefit from 7 nm next year, is threatening to switch to TSMC. Historical partner of Qualcomm, of which it will manufacture the next 5G modems, Samsung could keep control. But a partnership is nothing when tens of billions of dollars are based on nanometric optimizations: Apple did not hesitate for a second to abandon Samsung, after seven years of collaboration, in favor of TSMC.

The Taiwanese founder has been producing iPhone chips since the A8, and should produce the future A12, which will consume 40% less energy at equal power thanks to the 7 nm process. Better: with its new encapsulation technologies, TSMC opens up new design perspectives for Apple, favoring the stacking of circuits on top of each other rather than their spreading on a motherboard. Enough to free up space to integrate new components or enlarge the batteries… provided that TSMC maintains the technological course.

But just as the colossi of yesteryear are today's feet of clay, today's winners could be tomorrow's losers. TSMC had largely missed the 20 nm, Intel is struggling to finalize its 10 nm process, Samsung has taken the 7 nm train late. CC Wei, the president of TSMC, seems to be temporizing when he says that the future 5nm process “will be very long and very useful and very profitable”. But Samsung wants to believe in its ability to move technological mountains, and not only to win the 5 nm battle from 2020, but to open the 3 nm front in stride. The nanometer race is getting tougher and tougher, but it's not over.

Sometimes in the form of alloys, such as silicon-germanium notably used by IBM. Other materials can be used as needed, such as gallium arsenide for infrared diodes or photovoltaic cells. A wafer used to fit in the palm of your hand, but most foundries now use wafers 30cm in diameter and 775µm thick, with the number of chips produced per wafer increasing faster than the cost of producing the surface extra, at least up to a point.↩

Even if “fineness of engraving” and “component size” were largely synonymous until the beginning of the 2000s, and still remain intimately linked, greater fineness of engraving makes it possible to produce smaller components. If the words "source" and "drain" bring back memories and the subject interests you, read this file from Tom's Hardware, admittedly dated but still very relevant.↩

In a way so summarized that it ignores topographical improvements and the different types of transistors, it can be said that the reduction in the size of the transistors goes hand in hand with a reduction in the surfaces of energy loss, as well as a reduction in the operating voltage. The circuits consume less and release less heat at a constant number of transistors, or have a greater number of transistors and finally a greater computing power at equal consumption.↩

DIRECT. Assassination of Razia Askari in Besançon: "No guilt, no remorse, lack of empathy", the profile of Rashid Askari, accused of the assassination of his wife, dissected

[Video] The Amazing Spider-Man 2: the ultimate trailer

Samsung AU9000 Test | TechRadar

Nantes. He had assaulted a tram driver: sentenced to 6 months, he avoids prison