10 nm, 7 nm, 5 nm… les fondeurs n’en finissent plus de réduire la « finesse de gravure » des transistors. Ce petit chiffre est d’une grande importance dans la guerre technologique et commerciale qui oppose les fondeurs, attisée par les demandes de clients toujours plus exigeants. TSMC semble avoir remporté la bataille du 7 nm, dont il vient de commencer la production en volume, et dont la future puce Apple A12 devrait profiter. Ce qui ne veut pas dire que le fondeur taïwanais gagnera la guerre…

La fabrication de circuits intégrés est un processus lent et complexe, qui commence avec un wafer, un disque de silicium extrêmement pur1. Dopage, déposition d’une couche de résine, gravure, traitement thermique, revêtement par couche mince, découpe, encapsulation… la transformation du wafer en puces exige des dizaines d’étapes. La gravure est le moment le plus important : les composants sont « sculptés » ou « dessinés » par divers procédés, comme le traitement chimique du substrat de silicium, ou la photolithographie d’une fine couche de résine photosensible.

Le perfectionnement des techniques de gravure permet de concevoir des composants toujours plus petits. Attention toutefois : lorsque l’on parle de « finesse de gravure de 10 nm », on parle seulement du procédé de fabrication, et pas de la taille des composants2. Une même finesse de gravure de 10 nm produira des composants de taille différente selon les technologies employées et le type de composant. Les composants produits avec le processus 7 nm de TSMC, par exemple, ne sont pas beaucoup plus petits que ceux produits avec le processus 10 nm d’Intel.

Mais peu importe : tous les fondeurs, qu’ils utilisent tel ou tel processus avec tel ou tel matériau pour tel ou tel usage, travaillent à réduire la finesse de gravure. Il ne s’agit pas seulement d’augmenter la rentabilité d’un wafer, mais aussi et surtout d’augmenter la densité et le rendement énergétique des puces3. L’Apple A11 Bionic compte 4 300 000 000 de transistors, 1 869 565 de fois plus que le premier microprocesseur, l’Intel 4004. S’il était toujours gravé à 10 µm, il couvrirait la surface d’un grand salon, mais puisqu’il est gravé à 10 nm, il mesure moins de 90 mm^2.

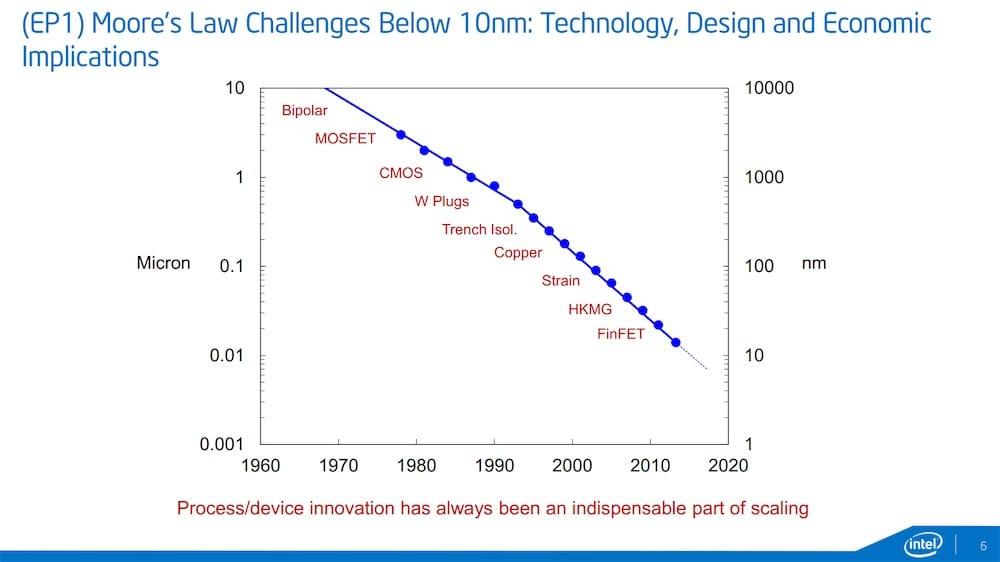

Chaque réduction de la finesse de gravure forme un processus, ou node, aux contours définis par l’International Technology Roadmap for Semiconductors (ITRS). Pourquoi passe-t-on de 22 à 14 nm, de 14 à 10 nm, de 10 à 7 nm ? Parce que l’ITRS veut suivre un rapport de √1/2 pour un, qui correspond au doublement du nombre de composants à surface égale. Définissez un nouveau node tous les deux ans, et vous pouvez continuer à faire passer les prédictions de Gordon Moore pour une loi intangible. Sauf que ce rythme est de plus en plus difficile à tenir.

Le passage sous les 22 nm a demandé l’abandon des transistors planaires, au profit de « transistors 3D » comme les FinFET. Le passage sous les 7 nm passera sans doute par l’utilisation de nouveaux transistors FinFET ou des transistors GAA, voire l’abandon du silicium. Les fondeurs commencent à buter sur des limites physiques, comme l’effet tunnel, et vont bientôt travailler à l’échelle de l’atome. Les recherches sur les transistors atomiques, et plus loin sur l’électronique quantique, n’en sont qu’à leurs balbutiements.

Mais revenons au présent. Intel tient à finaliser son processus 10 nm, désormais prévu pour la fin 2018 voire 2019. Le fondeur de Santa Clara est clairement en retard sur sa roadmap, qui prévoyait le passage à 10 nm pour la fin 2016, mais pas (encore) distancé par le reste de l’industrie. À processus égal en effet, les technologies d’Intel produisent des circuits plus denses que les technologies concurrentes. À condition de capitaliser sur l’expérience acquise pour rentabiliser le 10 nm et faire évoluer le 7 nm, Intel pourra rester dans la course.

Mais ses concurrents imaginent déjà mettre en production des processus 5 nm dès l’an prochain. Samsung a fait le pari de finaliser son processus 7 nm plus tardivement que ses concurrents pour éprouver la photolithographie à rayonnement ultraviolet extrême, qui sera impérative au développement des processus 5 nm, et ainsi prendre l’ascendant sur TSMC et GlobalFoundries. Le terrain libre, ces deux-là se sont livrés une bataille acharnée sur le 7 nm : TSMC l’a emporté et devrait récupérer les contrats de fabrication de processeurs et de cartes graphiques AMD.

L’autre grand match se joue sur le terrain du mobile, toujours avec TSMC, mais cette fois contre Samsung. Qualcomm, qui veut bénéficier du 7 nm dès l’an prochain, menace de passer chez TSMC. Partenaire historique de Qualcomm, dont elle fabriquera les prochains modems 5G, Samsung pourrait garder la main. Mais un partenariat n’est rien lorsque des dizaines de milliards de dollars reposent sur des optimisations au nanomètre près : Apple n’a pas hésité une seconde à abandonner Samsung, après sept ans de collaboration, au profit de TSMC.

Le fondeur taïwanais produit les puces de l’iPhone depuis l’A8, et devrait produire le futur A12, qui consommera 40 % moins d’énergie à puissance égale grâce au processus 7 nm. Mieux : avec ses nouvelles technologies d’encapsulation, TSMC ouvre à Apple de nouvelles perspectives de conception, en privilégiant l’empilement des circuits les uns au-dessus des autres plutôt que leur étalement sur une carte-mère. De quoi libérer de l’espace pour intégrer de nouveaux composants ou agrandir les batteries… à condition que TSMC maintienne le cap technologique.

Or de la manière que les colosses de jadis sont les pieds d’argile d’aujourd’hui, les gagnants d’aujourd’hui pourraient être les perdants de demain. TSMC avait largement raté le 20 nm, Intel peine à finaliser son processus 10 nm, Samsung a pris le train du 7 nm en retard. C.C. Wei, le président de TSMC, semble vouloir temporiser lorsqu’il dit que le futur processus 5 nm « sera très long et très utile et très rentable ». Mais Samsung veut croire en sa capacité de déplacer des montagnes technologiques, et non seulement de remporter la bataille du 5 nm dès 2020, mais d’ouvrir le front du 3 nm dans la foulée. La course au nanomètre est de plus en plus difficile, mais elle n’est pas finie.

Parfois sous la forme d’alliages, comme le silicium-germanium notamment utilisé par IBM. D’autres matériaux peuvent être utilisés selon les besoins, comme l’arséniure de gallium pour les diodes infrarouge ou les cellules photovoltaïques. Un wafer tenait autrefois dans la paume de la main, mais la plupart des fondeurs utilisent désormais des wafers de 30 cm de diamètre et 775 µm d’épaisseur, le nombre de puces produites par wafer augmentant plus rapidement que le coût de production de la surface supplémentaire, du moins jusqu’à un certain point.↩

Même si « finesse de gravure » et « taille des composants » étaient largement synonymes jusqu’au début des années 2000, et restent toujours intimement liées, une plus grande finesse de gravure permettant de produire de plus petits composants. Si les mots « source » et « drain » vous rappellent des souvenirs et que le sujet vous intéresse, lisez ce dossier de Tom’s Hardware, certes daté mais encore très pertinent.↩

D’une manière tellement résumée qu’elle ignore les améliorations topographiques et les différents types de transistors, on peut dire que la réduction de la taille des transistors va de pair avec une réduction des surfaces de déperdition énergétique, ainsi qu’une diminution de la tension de fonctionnement. Les circuits consomment moins et dégagent moins de chaleur à nombre de transistors constant, ou possèdent un plus grand nombre de transistors et finalement une plus grande puissance de calcul à consommation égale.↩

DIRECT. Assassinat de Razia Askari à Besançon : "Pas de culpabilité, ni de remords, manque d'empathie", le profil de Rashid Askari, accusé de l'assassinat de sa femme, disséqué

[Vidéo] The Amazing Spider-Man 2 : la bande-annonce ultime

Test du Samsung AU9000 | TechRadar

Nantes. Il avait agressé un chauffeur de tram : condamné à 6 mois, il évite la prison